In the rapidly advancing field of digital communications, high-speed Serializer/Deserializer (SERDES) technologies are crucial for enabling fast data exchange across various platforms. Despite their importance, the design and optimization of SERDES systems present significant challenges.

This blog post condenses Dr. Syed Bokhari’s webinar insights on specific challenges and solutions in high-speed SERDES design. With over two decades of experience as the Signal Integrity Architect at Fidus Systems, Dr. Bokhari shares targeted strategies such as maintaining signal integrity with advanced S-Parameter Analysis, combating electromagnetic interference through meticulous PCB layout optimization, and addressing ground plane resonance with strategic via placement. Highlighting techniques such as FPGA testing for dynamic data rate simulation and QSFP module troubleshooting, this video and blog offers targeted strategies for engineers to refine their high-speed digital communication projects.

Understanding High-Speed SERDES

High-Speed SERDES technology is a cornerstone of modern digital communication, enabling the rapid transmission of data across various platforms. At its core, SERDES is a pair of functional blocks in a high-speed transmission path that efficiently converts data between serial data and parallel interfaces in each direction. This fundamental technology underpins many of the digital communication standards we rely on daily, from the data centers that power the internet to the consumer electronics that permeate our lives.

Addressing challenges in High-Speed SERDES Design

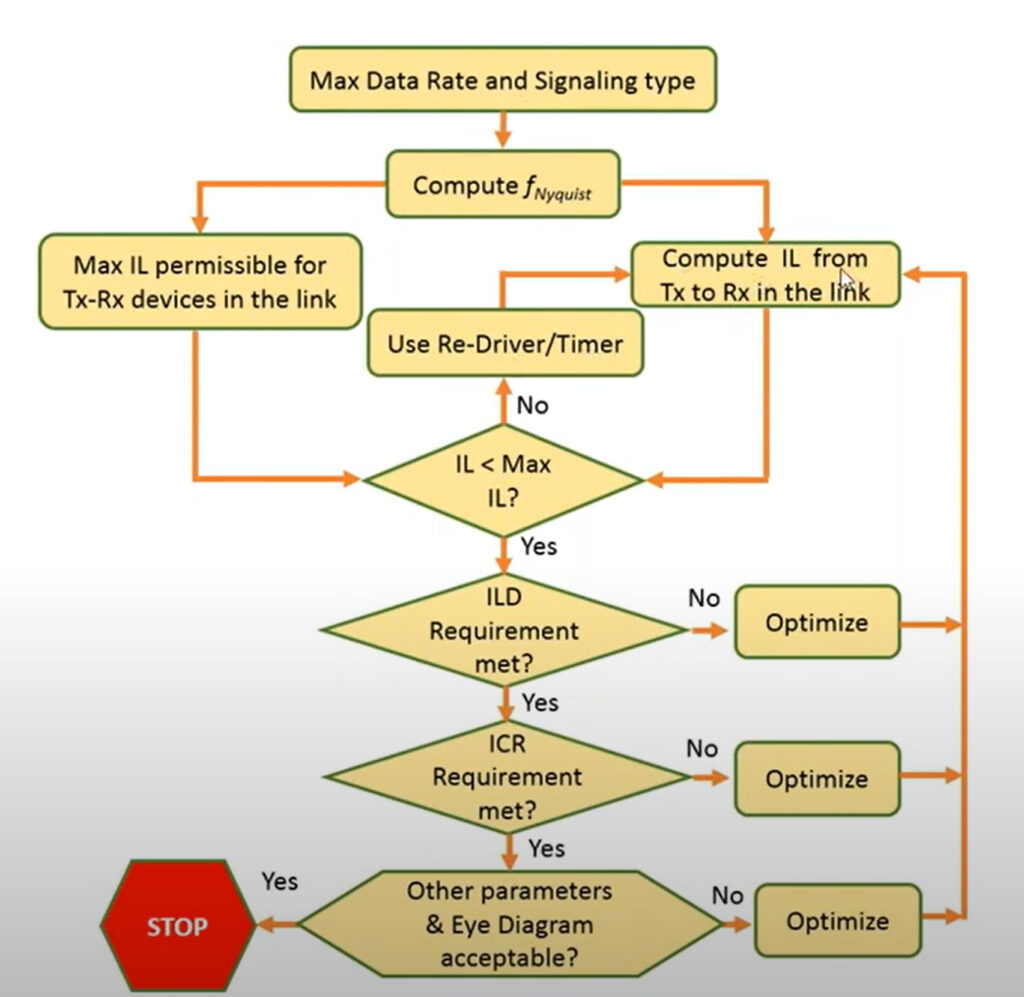

- Signal Integrity: A Critical Consideration: Signal integrity is paramount in high-speed SERDES design. It encompasses the quality and reliability of the electrical signals as they traverse through the PCB, connectors, and cables. Any degradation in signal quality, such as jitter, noise, or signal loss, can lead to errors in data transmission, impacting the overall system performance. Dr. Bokhari emphasizes the importance of accurate modeling and simulation in predicting potential signal integrity issues, allowing engineers to mitigate these challenges.

- Electromagnetic Interference: An Ever-present Challenge: As data rates climb, the susceptibility of SERDES systems to electromagnetic interference (EMI) increases. This phenomenon, particularly problematic at millimeter-wave frequencies, can lead to signal distortion and loss, complicating the design and optimization process. Managing these effects is crucial for maintaining signal integrity and ensuring the reliable operation of high-speed communication systems.

- The Critical Role of Ground Plane Resonance: Another significant challenge in high-speed SERDES design is ground plane resonance. This phenomenon can severely impact signal integrity, leading to unpredictable system behavior. Ground plane resonance occurs when the physical dimensions of the PCB’s ground planes or the layout of the ground vias create conditions for resonant electromagnetic modes. These resonances can couple unwanted energy into the signal paths, distorting the signals and degrading performance. Identifying and mitigating ground plane resonance is essential for achieving stable and reliable high-speed data transmission.

As we delve deeper into the complexities of high-speed SERDES design, it becomes clear that a comprehensive approach, blending theory with practical experience, is essential for overcoming these challenges. In the following sections, we will explore the solutions and debugging techniques that can address these issues, drawing on the insights shared by Dr. Syed Bokhari in the webinar.

Debugging High-Speed SERDES Designs Challenges

The leap forward in data transmission capabilities presents a unique set of challenges for engineers and designers working with high-speed SERDES technologies. Addressing these issues requires a blend of advanced debugging techniques, a solid understanding of signal integrity solutions, and a mastery of PCB design tailored for high-speed applications.

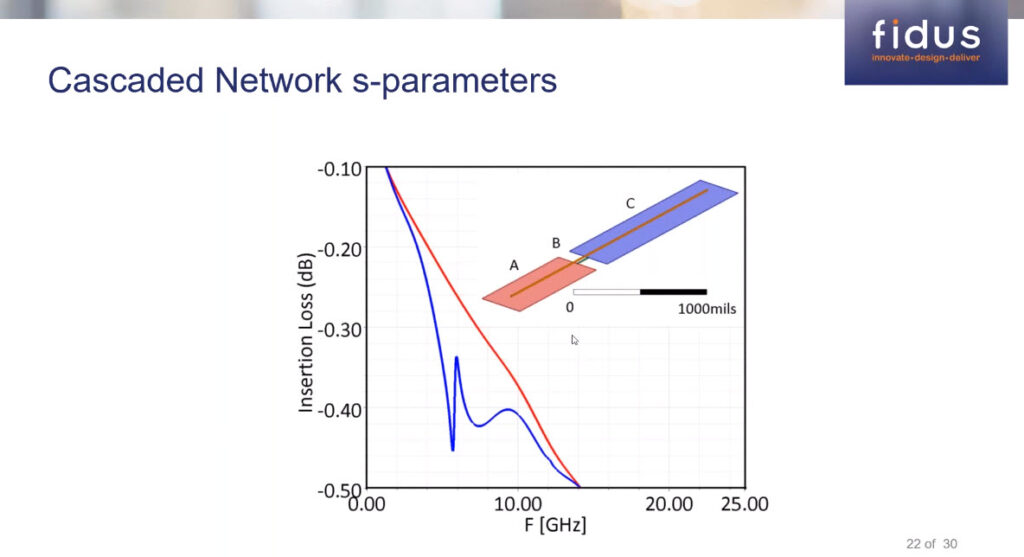

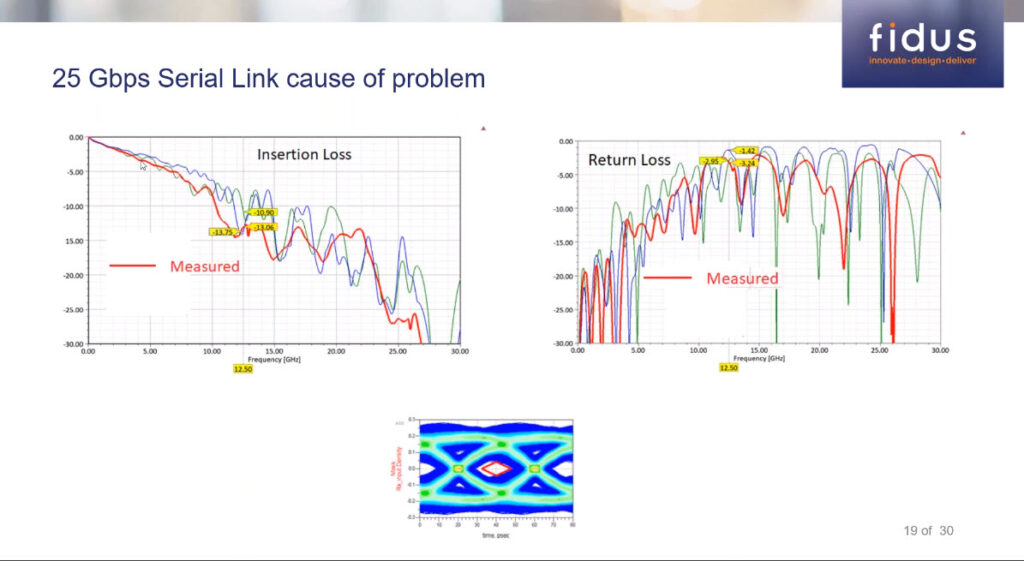

- Debugging Techniques for Signal Integrity: Signal integrity is the linchpin of successful high-speed data transmission, where even minor issues can have significant repercussions. Debugging techniques in this area often involves a combination of simulation and physical testing. By meticulously analyzing S-parameters, designers can gain insights into the behavior of high-speed signals within the PCB environment, enabling them to identify and rectify issues related to reflections, loss, and crosstalk.

- Mitigating Electromagnetic Interference: One of the most pervasive challenges in high-speed SERDES design is electromagnetic interference (EMI), which can degrade signal quality and reduce system performance. Dr. Bokhari’s approach to mitigating EMI involves a comprehensive understanding of the PCB layout and materials, as well as the application of shielding techniques and careful routing of signal paths. Additionally, leveraging advanced simulation tools to predict EMI’s impact and validate design choices is critical for ensuring that SERDES systems meet performance standards.

- Ground Plane Resonance: Detection and Mitigation: Ground plane resonance can adversely affect signal integrity, making its detection and mitigation a priority in high-speed SERDES design. There are several strategies for addressing ground plane resonance, including the optimization of PCB stack-up, the strategic placement of ground vias, and the use of high-quality PCB materials. By understanding the factors that contribute to resonance, designers can implement layout modifications that minimize its effects, ensuring stable and reliable data transmission.

- FPGA-Based Debugging for Flexibility and Precision: Field-Programmable Gate Arrays (FPGAs) offer a versatile platform for debugging high-speed SERDES systems. Their ability to simulate various data rates and patterns makes them an invaluable tool for identifying and resolving signal integrity issues. FPGA-based testing techniques allow for the dynamic adjustment of system parameters to isolate problems and verify solutions under real-world conditions.

- QSFP Module Troubleshooting-A Case Study: One of the webinars’ highlights was a detailed case study on troubleshooting Quad Small Form-factor Pluggable (QSFP) modules. Dr. Bokhari shared a systematic approach to diagnosing and resolving errors in these modules, emphasizing the need for a methodical analysis that considers both electrical and physical aspects of the design. This case study exemplifies the application of the discussed debugging and optimization strategies in a practical context, providing valuable insights into the complexities of high-speed SERDES troubleshooting.

Want to see the video? Jump to the webinar directly here.

Bridging Theory and Practice in High- speed SERDES Design

High-speed SERDES design intricately blends theoretical knowledge with practical application. This synthesis is crucial for addressing the nuanced challenges of SERDES technology, particularly as theoretical models often simplify complex electromagnetic and physical phenomena that can significantly impact real-world performance. Here, we delve into how engineers and designers can effectively bridge the gap between simulation and reality, ensuring that high-speed SERDES systems not only meet theoretical standards but also perform reliably in practical applications.

- Simulation vs. Reality – Understanding the Limitations: One of the pivotal discussions in the webinar centered on the discrepancies that often arise between simulation results and actual performance. Simulation tools, indispensable in the design process, provide a controlled environment to predict how high-speed SERDES designs will behave. However, as Dr. Bokhari highlighted, these tools typically rely on approximations and idealized conditions, which may not fully account for all real-world variables. For instance, the impact of PCB material properties, manufacturing tolerances, and environmental factors can lead to performance deviations that simulations may not predict accurately.

- Advanced Simulation Tools – Narrowing the Gap: To mitigate the discrepancies between simulated and real-world outcomes, use of advanced simulation tools offers more sophisticated models of electromagnetic behavior and signal integrity issues. Tools like 3D electromagnetic simulation software can provide deeper insights into how signals interact with the physical layout of the PCB and its environment, capturing effects like electromagnetic radiation and resonance with greater accuracy. By incorporating these advanced tools into the design process, engineers can develop more reliable SERDES designs that closely align with their simulated performance predictions.

- Empirical Testing and Validation – The Ultimate Arbiter: While advanced simulations play a critical role in SERDES design, Dr. Bokhari emphasized the irreplaceable value of empirical testing and validation. Laboratory testing and field trials offer concrete data on how a SERDES system performs under actual operating conditions, allowing designers to identify and address issues that simulations may not reveal. Techniques such as time-domain reflectometry (TDR) and vector network analysis (VNA) are vital for measuring signal integrity parameters accurately and verifying that the design meets its intended specifications. This hands-on approach ensures that the SERDES system can withstand the rigors of real-world application, from data centers to consumer electronics.

- Iterative Design – A Path to Optimization: The process of bridging theory and practice in high-speed SERDES design is inherently iterative. How findings from empirical testing feed back into the design cycle, informing adjustments and refinements to the SERDES configuration. This iterative loop—design, simulate, test, and refine—allows engineers to incrementally improve the system, optimizing performance and reliability with each iteration. It’s a dynamic process that leverages both the predictive power of simulations and the empirical evidence of testing to achieve the best possible outcomes.

The Future of High-Speed SERDES Design

The challenges and solutions discussed throughout the webinar not only provide a roadmap for current projects but also hint at the evolving landscape of digital communication. As data rates continue to increase, the need for innovative approaches to signal integrity, electromagnetic interference mitigation, and design optimization becomes ever more critical.

The future of SERDES design promises exciting developments, from new materials and manufacturing techniques to advancements in simulation software and testing methodologies. These innovations will likely address current limitations, offering improved performance, efficiency, and reliability for high-speed data transmission systems.

The quest for optimization in SERDES design is an ongoing journey. As we push the boundaries of what’s possible, continuous learning and adaptation will be key. Engineers and designers must stay abreast of the latest research, tools, and best practices to navigate this evolving field successfully.

Don’t miss the opportunity! Watch the Webinar and advance your high-speed design and debugging expertise today.

Watch now