Back to top

Discover Key Techniques for Optimizing Chip Packaging in High-Speed Data Transmission

WEBINAR RECORDING ON-DEMAND

Welcome to an insightful exploration of high-speed data transmission optimization, presented by Dr. Syed Bokhari of Fidus Systems. In this webinar, we delve deep into the intricacies of chip packaging and how it plays a pivotal role in enhancing the performance and reliability of high-speed data systems. As data transmission speeds soar into the extreme high-frequency range (beyond 50 GHz), traditional design approaches can introduce signal integrity problems that cripple system performance. This webinar equips you with the knowledge and techniques to overcome these challenges and achieve optimal chip-package interconnect performance.

- Speaker: Dr. Syed Bokhari, Signal Integrity Architect, Fidus Systems

- Date Published: February 13, 2024

- Duration: 20 Minutes

Key Topics Covered:

- Chip Packaging Optimization: Learn how innovative chip packaging techniques can significantly improve the performance of high-speed data systems. Discover the latest trends and technologies that are shaping the future of electronic design.

- Challenges in PCB Signal Integrity: Understand the critical importance of maintaining signal integrity in PCB design. Dr. Bokhari discusses common challenges and provides practical solutions to ensure reliable and efficient data transmission.

- S-Parameter Simulation Techniques: Gain insights into the use of S-parameter simulation tools to predict and optimize system behavior. This segment covers advanced simulation techniques that help engineers validate their designs and make informed decisions.

- Real-World Applications (Case Study) : The webinar features real-world case studies and examples from Fidus’ own portfolio of customer work that illustrate the application of discussed techniques in actual product development scenarios. These examples provide a practical perspective on how theories and strategies are applied to solve real industry challenges.

Additional Resources

- Learn more about Fidus’ signal integrity expertise here.

- Stay at the forefront of technology by participating in our upcoming series of webinars that cover innovative topics in the tech industry. Visit our webinar series page for more information and to register.

- Explore S-Parameter techniques on IEEE Xplore to learn simulation techniques used in high-speed data systems.

- Read about PCB design optimization techniques on e-power Journal.

Webinar Transcript

Introduction – 0:10

Good morning, everyone. Thank you for taking the time to attend this presentation. My name is Syed Bokhari. I work for Fidus Systems in Ottawa, Canada. Today, I’ll be talking about the optimization of chip packaging together with the PCB for improving the performance of the system.

The Current State of High-Speed Data Transmission

Let’s start with a simple question. This is something that is reasonably well known, but the impact of these assumptions is quite significant, especially focusing on frequencies that are extremely high. So, the current state of the art in bandwidth for signaling is about 224 gigabits per second. At these high frequencies, we’re talking about Nyquist frequencies in the range of 60 gigahertz.

Hypothetical Scenario: Cable Impedance

Some things that we tend to take for granted are becoming important. Let’s start with the simple question. If you’re given two 50 Ohm cables blindly without asking what those cables are, and if you connect them together, what would the impedance of the new cable be? Would it be 50 ohms?

Addressing Common Misconceptions

Now, what kind of answers should we anticipate? There are possibly three answers to this question. Some of you will choose to say yes. Some may choose to say no. And a more diplomatic answer would be it depends.

Role of Simulation in Validation

Let’s rephrase this question differently. So, just keep this in mind that let’s do a simulation. Instead of asking the question in terms of the cables, I’ll give you two S-parameter files and tell you that they belong to different 50 Ohm cables. I’m asking for a simulation. Run a simulation. And from the simulation result, can you tell me if the impedance of the cable will be 50 ohms?

So, let’s see what a simulation will do. A simulation would hook them up in cascade; as the S-parameter files are easy to hook up in cascade, two 50 Ohm S-parameter files will give you a 50-ohm impedance. There is no question there. So, the answer from the simulation is unique. But the answer without looking at the simulation can be very different.

Real-World Implications

And here’s the reason why it will be different. Those who said yes would have probably imagined the cables identical. That’s a good assumption. Otherwise, you can’t connect them easily. So, two identical 50 Ohm cables hooked up together would give you 50 ohms. The simulation will also show you 50 ohms; there’s no question. Those who said no probably assume that in general, two 50 Ohm cables don’t have to be identical; you can have a very thin coax and a very thick coax too. So, in which case even if you succeeded in making them somehow, there is an impedance discontinuity at the junction and that would not necessarily give you 50 ohms over a very wide frequency. So, that would be the reason why you’d say no.

The Complexity of Impedance Matching

And those who said, it depends, would be like, okay, you can’t just join two cables together. And so, you will need some kind of a taper mechanism. Once there is a taper, it becomes a question of frequency dependence; at certain frequencies, it’ll still be 50 ohms, at very high frequencies, it won’t be so.

Discrepancies Between Theory and Practical Outcomes

So, all the answers are different. But note that the simulation, the answer that you get from simulation, is always unique, and that says 50 ohms. So, what do we learn from this? If we simplify S parameters of cascaded networks, the theory is fairly accurate. It becomes an approximation in the electromagnetic sense. You cannot blindly apply cascade theory without really having an idea about what the physical problem looks like.

The Importance of Proper Port Placement in Simulations

And this is one important thing to remember about cascading S parameters; it is a great tool. It simplifies a lot of things, but there are frequencies where, especially the very high end, it introduces an error. The next thing that we noticed is when you simulate a complex structure, we need to, in order to obtain impedances, we need to define ports. Ports have to be placed at some points, and they cannot be placed arbitrarily, especially it is good to place ports at a uniform transmission line section to end where you place the port; it should be uniform on both directions from the port. And that is probably the most ideal location for a port. You can, in theory, place a lumped gap port anywhere you please. But for very high frequencies, it should be at a place where the fields are well-behaved and best at a transmission or the transmission line location.

Overview of Chip-Package Interconnect Optimization

So, with these two cases, let me start my presentation on chip-package interconnect optimization. The prelude was mostly to lead to exactly what is being done here to optimize a chip-package interconnect. Now, again, like I mentioned, we are talking about really, really high frequencies, as the Nyquist is in the range of 50 gigahertz.

Critical Parameters: Insertion Loss, Return Loss, and Crosstalk

Plus, that’s where these approximations that we generally take for granted become problematic. So, what I’m optimizing in this chip-package interconnect is S parameters, obviously, these parameters. Now, most of these parameters that we really care about are the insertion loss, the return loss, and the crosstalk. As far as the insertion loss goes, there’s very little one can do about it, especially when you’re dealing with an IC system that has constraints on how thick or how wide a trace can be and how lossy was the loss of the substrate.

Optimizing Return Loss

Let’s assume we pick the best of the best; your insertion loss is going to be limited by the trace length, trace width; not a lot you can do. The return loss, on the other hand, is significant. Return loss affects the insertion loss deviation. And so, it is really critical that you optimize the return loss as best as possible so that the insertion loss is smooth and helps in the error-free transmission.

Simulation and Package Design

And we also have a category of crosstalk. I’ll not be going into addressing crosstalk here; crosstalk deals with the system of naps and how you isolate them. So that’s not being considered here. So, the focus is primarily on return loss of a very high-speed data transmission. And the simulations again are done using ANSYS HFSS, which is a 3D the full 3D EM solver version. So, let’s take a look at what a package looks like and how we simulate a chip package. This is a typical package; it has, it’s one of the more popular ones; there are other types of packages, students call it an organic package, and it comprises the core tech core and a number of prepreg laminate type layers, and the certificate structure is a flip chip. So, there will be there. There are solder bumps on the chip on the die side and BGA balls on the PCB side. If we look at this package closely, for most applications, we generate the S-parameters of this package by simulating the circuit that I’ve shown here; ports are placed on a reference plane, usually on a reference plane. That is defined on the die side and another reference plane on the package side; ground balls provide the return path continuity on both sides. And this is generally simulated, and this works very well for even up to clarified gigahertz. So, but as the frequency starts increasing, it doesn’t, this approach gives you the S-parameters all the way up to the BGA balls. It, the BGA, that the package eventually needs to get integrated with the PCB. The PCB itself would have pads that would connect to the balls. So, at the interface between the package and the PCB, there’s a discontinuity. So, if you notice here how the ports are defined. The ports on that die side, on the die bumps, these are very small, usually typically they are like 35 microns in radius, maybe 90 microns in height for the frequencies we deal with. It is acceptable to use the S-parameter, the port definition, by placing the port on the die on a die bump without sacrificing the accuracy too much. Otherwise, it gets extremely complicated to have a port on the die within the diagnosing insect that died. So, this is acceptable because the structure is small.

Challenges and Solutions in High-Frequency PCB Design

But when we look at the BGA bumps, these are typically one; they could have a pitch of one mm; they’re about 600 microns tall, about 500 microns wide; these are big structures, and placing a port at a reference plane near the BGA balls to the PCB interface is questionable; this will violate some of the fundamental limitations of S-parameter definition. So, what yet, this is how when we asked for a package Model S-parameter model, this is what is done, and they give it; this model gives us your, you take this model, and you integrate it with the rest of the PCB and proceed. It’s good, it’s a very good approximation up to very fairly high frequencies. But if you’re talking 50 gigahertz plus, the process tends to break down, and you’ll need to consider the entire structure as a whole. Now here’s what a composite chip package PCB stackup looks like; you have the package stack up is different from a PCB; the PCB generally has the mix of layers, prepreg, scores; in packages, it is inevitable the use of multiple levels of blind vias becomes inevitable. So, you will have a number of what in the PCB terms we call prepreg layers; there’s usually a rigid core to provide them to provide rigidity to the package. And on both sides of this, you have a number of prepreg layers which are connected by stacking micro vias depending on the on the five that is used; they may have limitations on how many, how many, how many blind vias can be stacked? Usually, it’s five; you can’t stack more than five.

Simulation Practices

But that’s it; that the package five dependent thing. So, within those limitations, we go ahead and design a package. And then we interface the package to a PCB. But the frequencies that I’m talking about, we wouldn’t normally use backfilling on the PCB; it will be a blind as well. And we consider this in their example. For illustration, we just use the few layers or the top of PCB to get the interconnect optimized. Now there are sections here that before we started a full-fledged optimization, it’s a tedious exercise; there’s way too many variables involved. So it’s good practice to section the complex structure into pieces. Now one of the things we saw in the previous slide is stacked vias. Stacked vias typically have a geometry like what I’ve shown before; we assume that this is a uniform stack via geometry and optimize this individually so that we can see that we can then put them together and redo the final optimization. So, if you look at this example here, we have just a stack via geometry with ground vias on the sides is a nearly perfect coax you could call it, and the simulation with some optimized anti pad diameter and the end the location of the ground vias at a particular radius gives us a 40 dB type return loss at 200 gigahertz. So, this is probably the easiest test of the structures in a complex package. The second one is the, is the Korea that’s in the rigid section. It’s much longer than the micro vias. Again, it can be optimized to a certain extent; the results are not as good as the ones for a microvia. But you can see that is, you can still do fairly good up to 60 gigahertz; you can do better than 30 dB return loss up to 60 gigahertz. The last part is the BGA vias. Now here is, this is the bottleneck. Here is where you have very little or no control over anything. The BGA locations are decided by the pitch of the package. You only have Atmos the anti-pad on the package side and the anti-pad on the PCB side; pretty much those are the only two variables it could have some more ground vias in the package side but not on the PCB side. So, with this, this one, and here you can clearly see that it’s almost impossible to get anything better than 20 dB return loss beyond the board let’s say 30, 30 gigahertz, okay. Now if we put them all together, and so we want to optimize the whole, the entire structure, we need to integrate all of these pieces together, and we need to, we need to change the variables like we vary a few variables to get the best return loss for the entire structure which is an integration of the package and the PCB. One thing that we look for is the TDR of this package; we try to get a TDR response that is inductive and capacitive alternatively so that they tend to cancel out and give us a broadband impedance, and this is, this can be done in many ways to obtain this kind of response; we can vary the inductance, you can make one side more inductive, the other side more capacitive; it is to strike; we need to strike a balance where it gives you the optimal structure. So especially the result or here of a geometry that is optimized. So, we have, we have used the piecewise optimization idea. So, each one is optimized individually, and then we put them all together and optimize the entire structure as a whole. So, this way we keep the number of variables at a smaller value. And we limit the number of trials you need to do for a full 3D HFSS optimization. As you can see from the result, we can pretty much see that we could, we could potentially get the, the desirable 20 dB return loss perhaps up to gigahertz beyond that it is largely taken over by the BGA ball pitch and the size of the BGA balls. And clearly, this is, this represents a limitation in the best return loss that you can get integrated chip package structure that uses a one mm pitch BGA; if we reduce the pitch of the BGA like some of the packages that do the very high speed BAM for 200 Plus gigabits, they are, they’re likely to use the hawk and pitch BGA; this response will improve slightly, will improve slightly but can be improved to a slightly higher frequency, but essentially the limitations come from the BGA balls. So, with this, this result tells you that first of all, you do need to integrate the package and the PCB to obtain results that are accurate. If you notice here in the structure, we have transmission lines at both ends, and that’s where we placed the ports, way ports in this case. So that removes the error introduced by placing ports at discontinuities. So, we get this, this will be extremely accurate and it will be easily reproducible by measurement.

Conclusion

So, with this observation, I will come to some conclusions here. So, when we are dealing with complex structures that comprise the board and that comprise a PCB and package, we should review the complex structures visually before and decide where to place the ports; ports are best placed at the uniform transmission line sections. And that’s where, what gives us the best accuracy; so, in this case is fairly straightforward. Place the ports or the transmission line ends. We don’t have to go deep into the dissection because the die is, that die is electrically much smaller even at 60 gigahertz, so we could choose the transmission line on the package and place ports at that location. On the PCB side, the best place for the ports is the PCB trace location. Now, the optimization expense can be daunting because there’s way too many variables; there’s a PCB side and the package side, so it is easier to optimize the individual sections of each discontinuity like Korea, the blind via, the BGA cables, and even the transmission line. It could design the transmission line to give the desired impedance; optimize them, usually use them as a good starting point to optimize the end-to-end structure, and you perform the full optimization of the end-to-end setup. With this, I will stop the presentation. If you have any questions, I’ll be happy to answer them. Or you can reach out to me; I’m using my email to thank you again for attending the presentation.

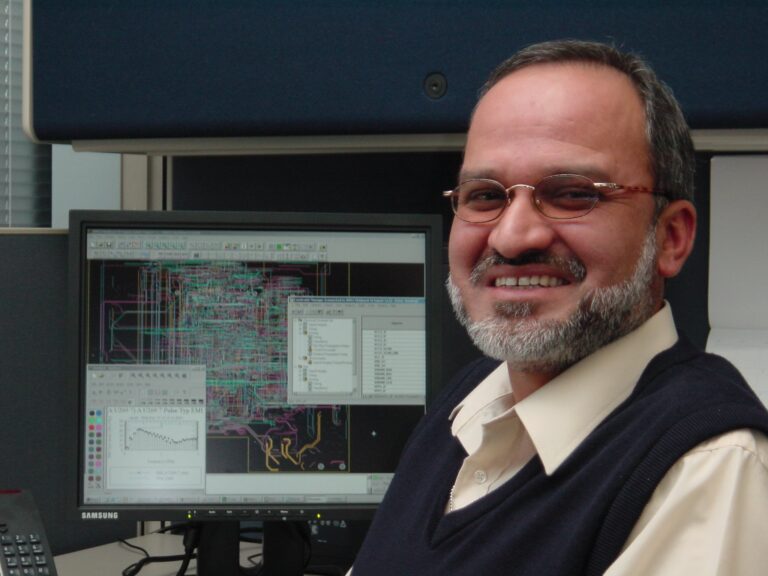

Speaker

Dr. Syed Bokhari at Fidus Systems, with over 20 years of experience, specializes in signal and power integrity, EMC, RFID antenna design, and numerical methods in electromagnetics. He was also one of the original developers of SPECCTRA Quest, a leading-edge SI analysis tool. Dr. Bokhari is a senior member of IEEE and since 2000 has been the Chairman of the Ottawa EMC chapter. With over 50 publications, he has contributed to several technical books and holds two patents. He received a Ph.D. degree in Electrical Engineering from the Indian Institute of Science, Bangalore, India.